クロックまわり下調べ

Z80の動作の理解にあたって手動クロックで各マシンサイクルを追いかけていこうと思っているので、そのために調べたことをメモ。

資料を読んでいると「nMOS版は最低クロック周波数がある」という記述あり。WikipediaによるとnMOS版はダイナミック・ラッチという機構を使っているのでクロックを止められないとのこと。

Unlike the original nMOS version, which used a few dynamic latches, and therefore could not be stopped for more than a few thousand clock cycles.

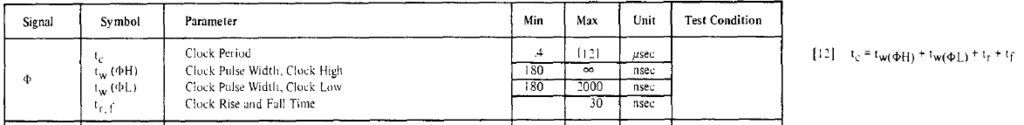

で、ダイナミック・ラッチというのはDRAMのメモリセルのようなものらしい。要するにコンデンサを使って情報保持してるからリフレッシュが必要? データシートでAC特性を調べると、tw(φL) max = 2000[nsec] がこの辺の事情を表してそう(電荷が抜けるので一定時間以上Lにできない)。

でもパルスをHにできる時間は∞なので、一応クロックを止められるような気はする。ボタンを押すごとに1μsecくらいのパルスを出す回路を作って実験してみよう(555が使えそうだけど、こんなに短い時間のパルスも出せるのかな…)。

- 【追記】555だと出力パルス幅より短い入力トリガを与えないとダメっぽい(時定数コンデンサが充電されて内部F/FのRがHになる時、トリガパルスが終わってないとSもHのままなので)。74HC123がデータシートによるとnsオーダーの単発パルスを出せるようなので買おう。

ちなみに↑のZ80のデータシートは2.5MHzのものですが、4MHzでもmax側の値は同じのようです。